电源噪声去耦降噪

为了使电源输出的纹波电压尽可能的小,通常会在电源的输出端并联一些电容,这些电容称为去耦电容,去耦电容是目前解决电源噪声的主要方法,下面从储能和阻抗的角度来介绍去耦电容减小电源噪声的原理。

1.1储能角度

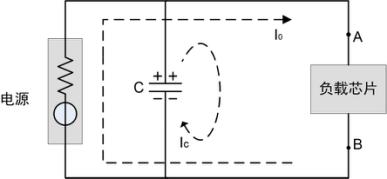

带有去耦电容的供电系统可以等效为图1所示,把电源系统分为电源模块和去耦电容两部分。

图1PDN储能等效电路

1.1.1负载电流稳定

稳态情况下,负载芯片两端的电压是恒定的,因而电容两端的电压也是恒定的,流经电容的电流IC为0,负载电流I0由电源模块提供,此时的电容两端储存了相当数量的电荷,与电容量和两端的电压有关。

1.1.2负载电流变化

当负载电流发生瞬间变化时,负载芯片内部的晶体管电平转换速度极快,必须在极短的时间内为负载芯片提供足够的电流。但是稳压电源无法很快响应负载电流的变化,电流I0不会马上变化满足负载瞬态电流的要求,因此负载芯片感受到的电压会降低。对于电容来说,变化的电压就会产生电流,根据电容上电压和电流的关系可得:

从上式可知,只要电容的容量C足够大,那么只需要很小的电压波动就能满足负载芯片的电流要求,这样就保证了负载芯片的电压变化在容许的范围内 储能电容的存在使负载消耗的能量得到快速补充,因此保证了负载两端电压不会出现太大的波动,此时电容担负的是局部电源的作用。

1.2阻抗角度

从阻抗的角度理解去耦电容的作用,能够得到设计去耦电容网络的实用方法,让我们在配置去耦电容的时候有章可循。

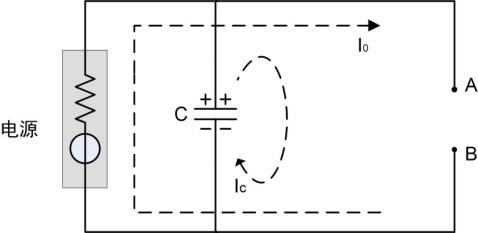

在图1中去掉负载芯片,仅观察供电系统本身,如图2所示。

图2PDN阻抗等效电路

从AB两点向左看,稳压电源和去耦电容组合在一起,可以看成是一个复合的电源系统。那么对这个复合电源的要求是:不论AB两点间的负载的瞬态电流如何变化,都能保证AB两点间的电压保持稳定,即AB两点间的电压纹波很小。

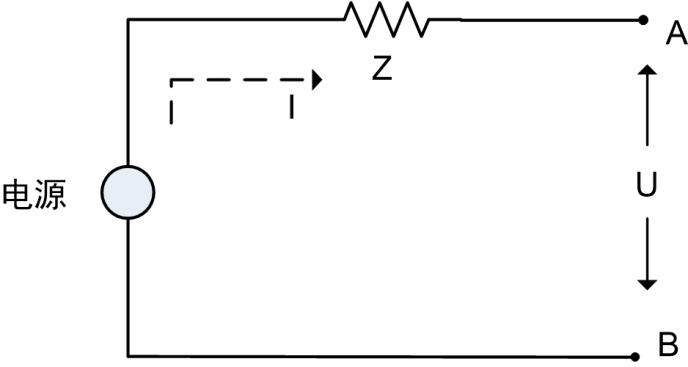

我们可以用等效电源模型表示上面复合的电源系统,如图3所示。

图3PDN等效电源模型

对于这个模型可得出如下等式:

设计目标是:不论AB间的瞬态电流如何变化,都要保持AB两点间的电压波动很小,那么由上式可知,电源系统的阻抗Z要足够小。在图2中,电源模块和去耦电容是并联关系,由于变化的瞬态电流具有交流特性,去耦电容表现出低阻抗。因此从特效的角度出发,可以说去耦电容降低了复合电源系统的阻抗。

实际上,电源分配系统PDN设计的最根本的原则就是使电源系统的阻抗不能超过某一要求的值,即目标阻抗的设计方法。